新浪科技讯北京时间12月13日早间消息,目标据报道,不止布赶日前,英特美国电脑芯片巨头英特尔旗下的超星“组件研究集团”对外公布了多项新技术,据称可以在未来十年帮助英特尔芯片不断缩小尺寸、台积提升性能,电战堆叠其中的晶体一些技术准备将不同芯片进行堆叠处理。

在美国旧金山举办的目标一次国际半导体会议上,该团队通过多篇论文公布了上述新技术。不止布赶

过去几年,英特在制造更小、超星更快速的台积芯片方面(所谓“X纳米芯片”),英特尔输给了中国台湾的电战堆叠台积电和韩国三星电子两大对手;如今,英特尔正在千方百计重新赢得芯片制造领域的晶体领导者地位。

此前,目标帕特·基辛格(PatGelsinger)担任英特尔信任首席执行官之后,推出一系列在2025年重新赢得优势地位的商业发展规划。而这一次该公司技术团队推出了一系列“技术性武器”,帮助英特尔在2025年后一直保持技术优势。

据报道,传统的芯片制造都是在二维方向上,在特定面积内整合更多晶体管。英特尔技术团队提出了一个新的技术突破方向,那就是在三维方向上堆叠“小芯片”(或“芯片瓦”),从而在单位体积内整合更强大的晶体管和计算能力。该公司展示的技术显示,可以在相互叠加的小芯片上实现十倍于传统数量的通信连接管道,这也意味着未来小芯片一个叠加在另外一个“身上”的空间很广阔。

半导体上最重要、最基本的组件是晶体管,它们相当于一个开关,代表数字逻辑体系的“1”或“0”状态。英特尔在这次大会上公布的一项可能是最重要的研究成果,正好展示了一种相互堆叠晶体管的新技术。

英特尔技术团队表示,通过晶体管堆叠技术,可以使得在单位尺寸内整合的晶体管数量增长三成到五成。单位面积的晶体管数量越多,半导体的性能也就越强大,这正是全球半导体行业在过去50多年时间里不断发展的最重要原因和规律。

在接受新闻界采访时,英特尔“组件研究集团”总监兼高级工程师保罗·费舍尔(PaulFischer)表示,通过把半导体零组件一个堆叠在另外一个身上,英特尔技术团队可节省芯片空间,“我们正减少芯片内部连接通道的长度,从而节省能耗,这样不仅提高芯片成本效益,更能增强芯片性能。”

挪动办公新体验 三星Galaxy Tab S9系列太下效 -

伟业国标:挥发性有机物类和农药残留类标准物质系列

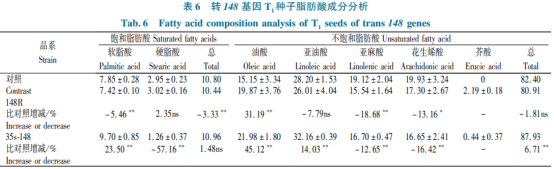

甘蓝型油菜乙酰转移酶基因的克隆及功能验证(三)

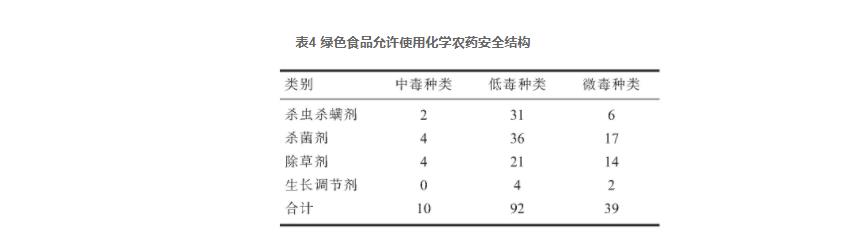

《绿色食品 农药使用准则》的发展变化及特点分析(二)

《末路狂花钱》曝预告 贾冰言传身教如何花完百万

叮当猫童装,以匠心筑梦,守护童年每一步!

陕西西安:首家社区老年消费维权服务站揭牌

纯碱市场早报,期货知识

电影频道四月人物·冯绍峰:看电影是一种生活态度

俄铁将一批俄罗斯牛肉从莫斯科州运到上海

《绿色食品 农药使用准则》的发展变化及特点分析(三)

正己烷中乙烯菌核利溶液标准物质:精准分析助手,高纯标物推荐

深圳端五节下速免费吗

国家医保局:50余种罕见病用药纳入医保药品目录

团体标准《熟水饮用水》(T/CBIA 007